Researchers at the Massachusetts Institute of Technology (MIT) have unveiled a new scalable superconducting memory array that significantly reduces error rates, paving the way for advancements in quantum computing. The breakthrough, detailed in a paper published on January 25, 2026, in the journal Nature Electronics, marks a crucial step toward developing faster and more energy-efficient memory components essential for complex computational tasks.

Superconducting memories, which utilize superconductors that conduct electricity without resistance at low temperatures, present a promising alternative to conventional memory technologies. They have the potential to enhance performance while consuming less energy. Yet, scaling these devices to incorporate multiple memory cells has proven challenging, primarily due to high error rates associated with existing designs.

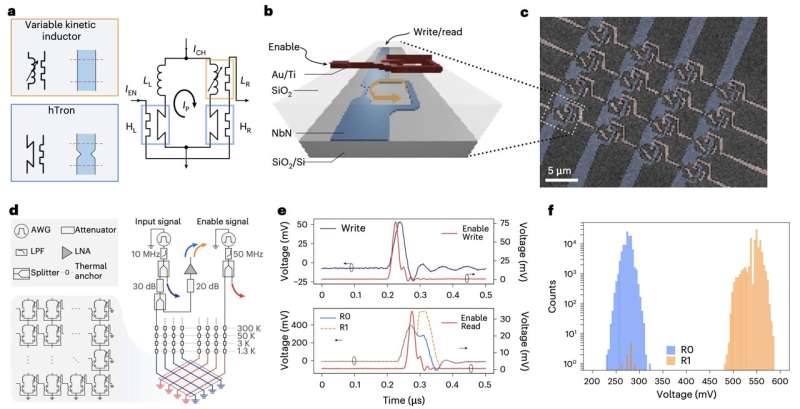

The MIT team, led by researchers Owen Medeiros and Matteo Castellani, focused on creating a memory system based on nanowires—one-dimensional structures that exhibit unique optoelectronic properties. Their new design features a compact 4 × 4 superconducting nanowire memory array, which boasts a functional density of 2.6 Mbit cm −2 and is designed for efficient row-column operations.

In their study, the researchers constructed each memory cell with a superconducting nanowire loop that includes two temperature-sensitive switches and a kinetic inductor. This configuration allows the array to operate at a temperature of 1.3 Kelvin, where they implemented multiflux quanta state storage and destructive read-out. By optimizing the sequences of write and read pulses, they achieved a remarkable reduction in bit errors while maximizing operational reliability.

The functionality of the memory array hinges on precise electrical pulses directed at individual cells. These pulses temporarily heat one of the nanowire switches, increasing its resistance and allowing a magnetic flux to be injected into the loop. This flux encodes data values (0 or 1), and once the pulse ceases and the nanowire returns to its superconducting state, the information remains trapped within the loop.

Initial tests of the new memory array revealed a noteworthy performance, with only one error for every 100,000 operations. This bit error rate of 10 −5 is significantly lower than that of many previously developed superconducting memories. The researchers also utilized circuit-level simulations to further analyze the dynamics and stability of the memory cells under varying conditions.

The implications of this research could be profound, potentially advancing the integration of superconducting memory systems into practical applications. As the design matures and scales, it may lead to the creation of more reliable and effective memory systems, essential for the future development of low-energy superconducting computers and fault-tolerant quantum computing architectures.

This groundbreaking study highlights the ongoing efforts in the field of quantum computing and superconducting technology, showcasing how innovative approaches can overcome existing limitations. The research team is optimistic that their advancements will contribute to the broader goal of achieving reliable superconducting memory systems, bringing us closer to realizing the full potential of quantum computing.